Digital Design & Comp. Arch. - Lecture 20: SIMD Processing (Vector and Array Processors) (Spring'21) - YouTube

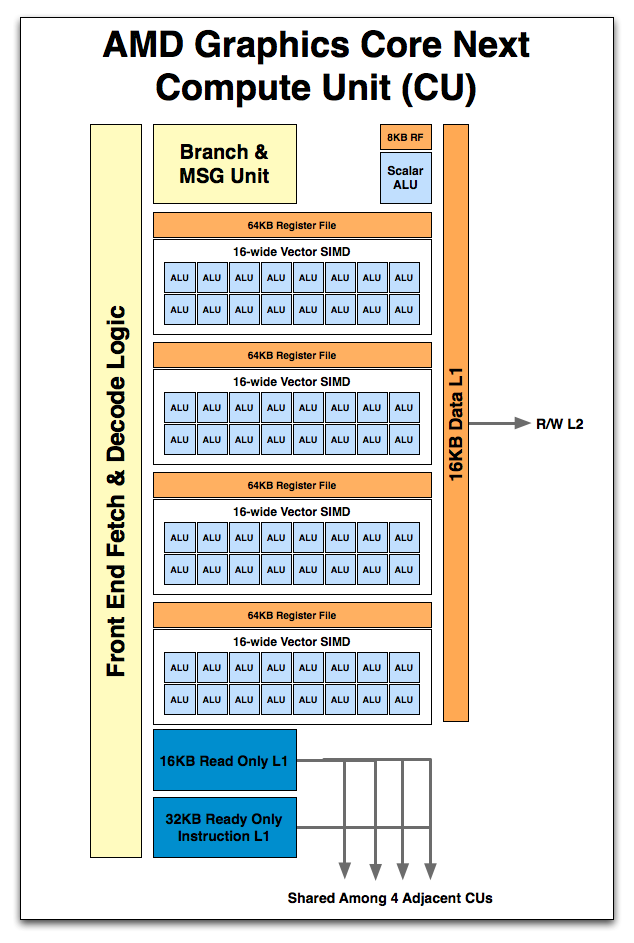

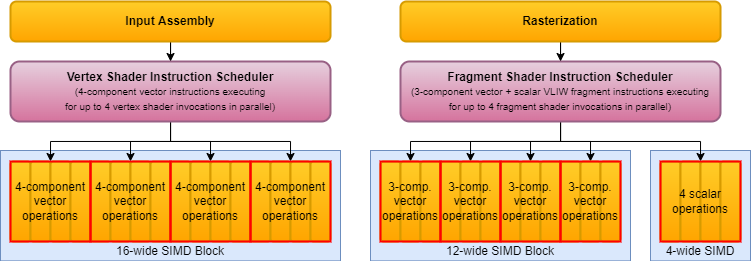

Many SIMDs Make One Compute Unit - AMD's Graphics Core Next Preview: AMD's New GPU, Architected For Compute

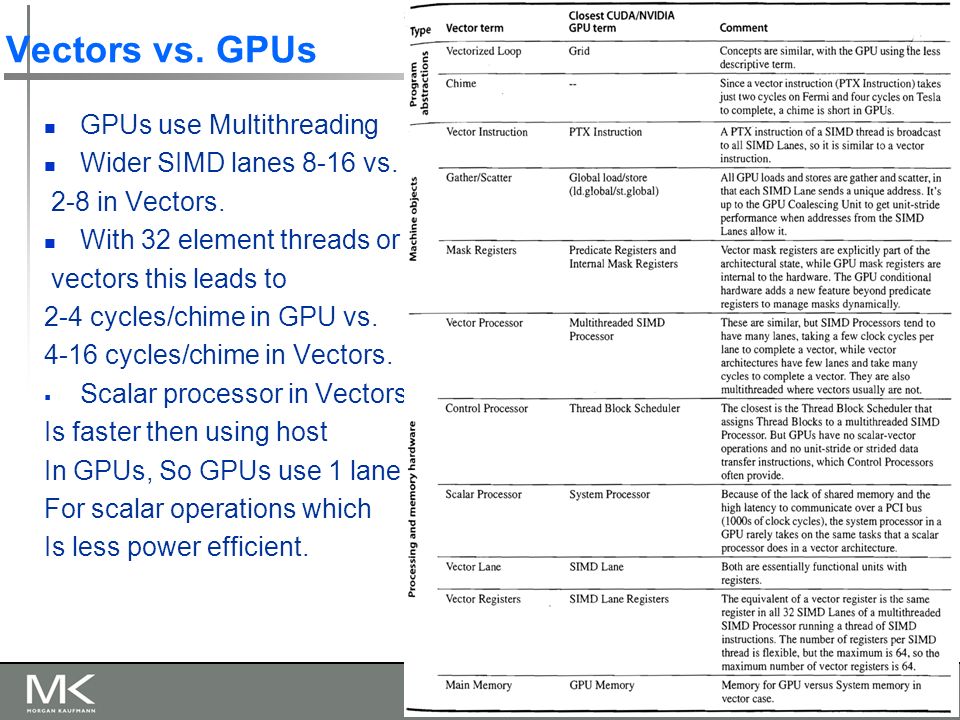

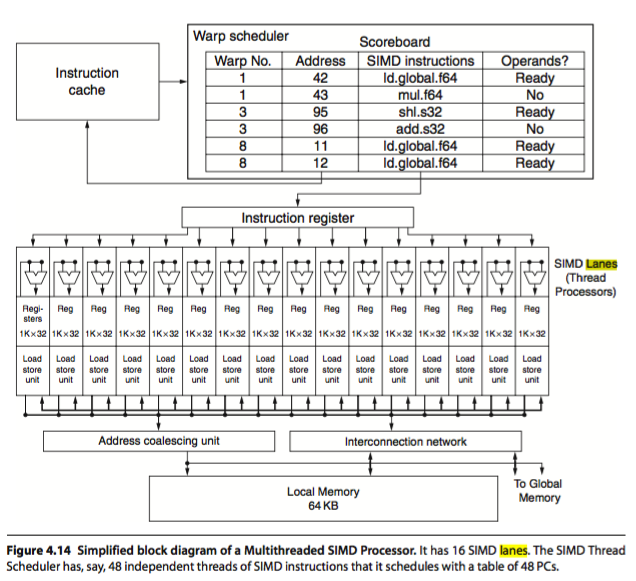

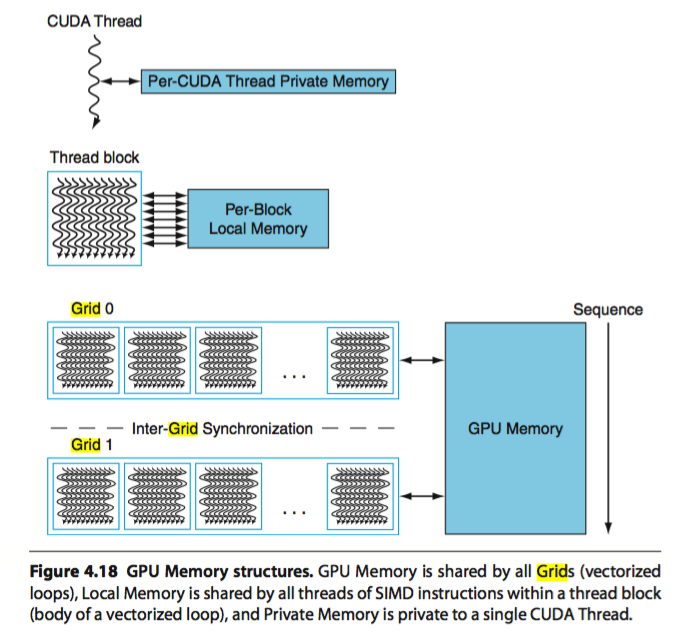

1 Chapter 4 Data-Level Parallelism in Vector, SIMD, and GPU Architectures Computer Architecture A Quantitative Approach, Fifth Edition. - ppt download

Appendix C: The concept of GPU compiler — Tutorial: Creating an LLVM Backend for the Cpu0 Architecture

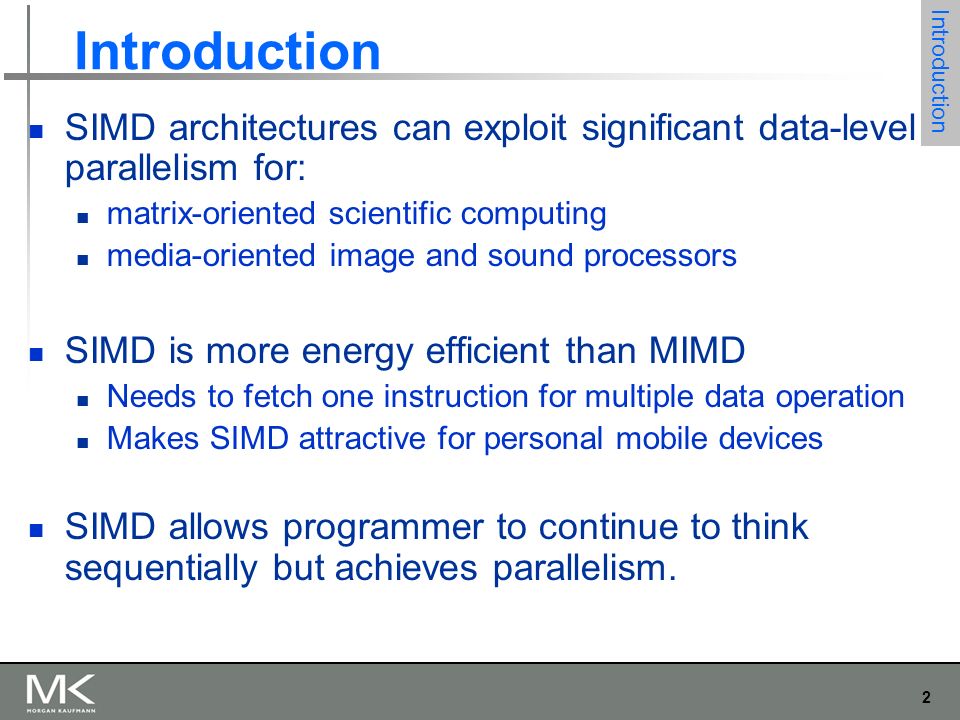

1 Chapter 4 Data-Level Parallelism in Vector, SIMD, and GPU Architectures Computer Architecture A Quantitative Approach, Fifth Edition. - ppt download

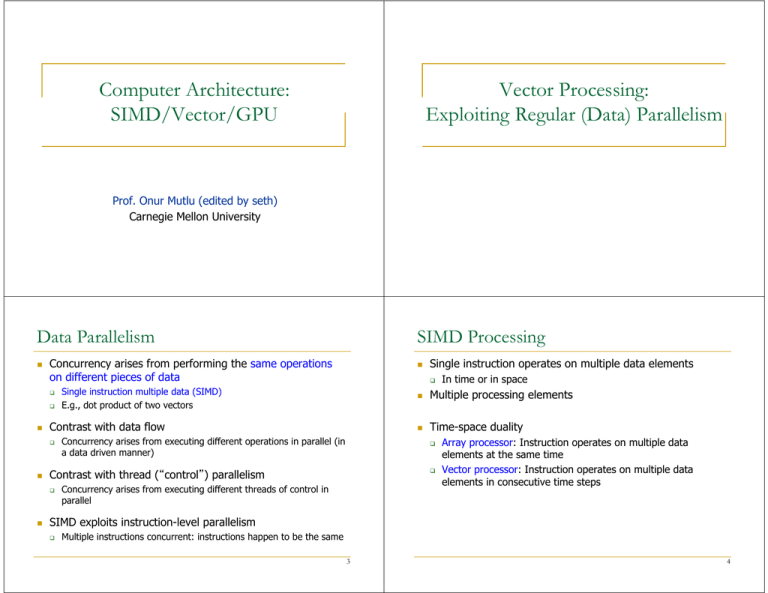

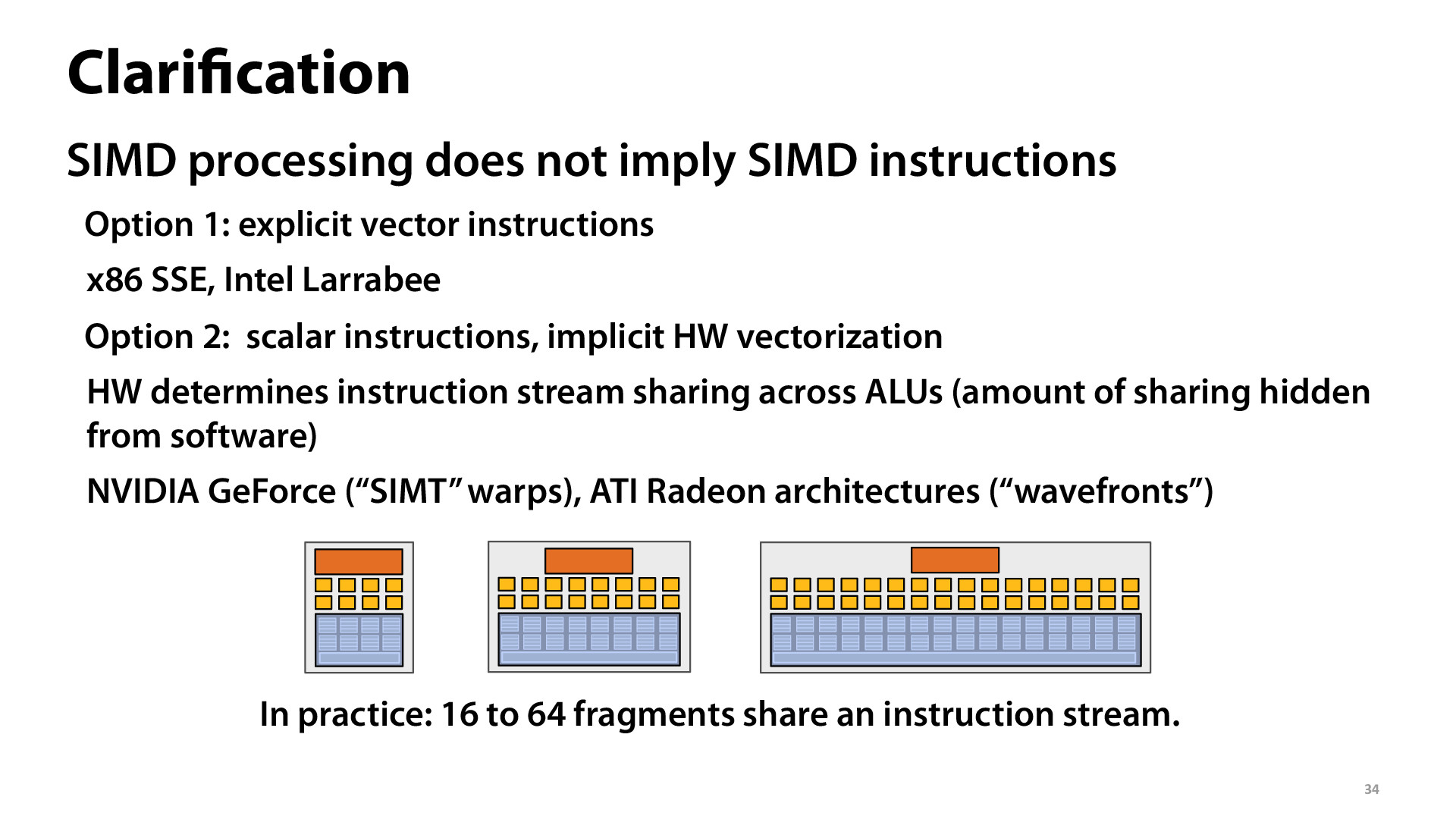

Concepts Introduced in Chapter 4 SIMD Advantages Vector Architectures Extending RISC-V to Support Vector Operations (RV64V)

![PDF] Scalar-vector GPU architectures | Semantic Scholar PDF] Scalar-vector GPU architectures | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/5982bf763c6387a9a12d950d01d3d4f8c90a2334/12-Figure1.1-1.png)